Difference between revisions of "DreamTurboCard (Spanish)"

(→Status register) |

(→Registro de estado) |

||

| Line 44: | Line 44: | ||

|- | |- | ||

!scope="row"|0 | !scope="row"|0 | ||

| − | |style="text-align:center"|EP RFSH|| | + | |style="text-align:center"|EP RFSH||el microcontrolador ha modificado la memoria NVRAM (el EP debería comprobarlo, y la lectura del puerto de datos NVRAM pondrá a cero este bit) |

|- | |- | ||

!scope="row"|1 | !scope="row"|1 | ||

Revision as of 18:02, 13 May 2018

Contents

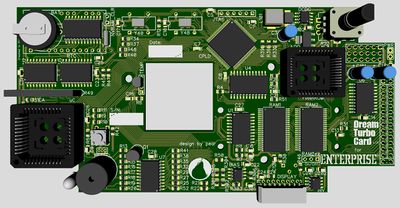

Breve información

Dream Turbo Card (DTC) es una placa de expansión interna que añade memoria RAM y FlashROM, reloj de tiempo real(RTC) y generador seleccionable de reloj de sistema y EXDOS.

Especificaciones

- 1 MB de SRAM, opcionalmente 2 MB, en bancos de 64KB,

- 512 KB de FlashROM, 8 bancos de 64 KB con opción de desactivación individual con EXOS siempre en el banco 7,

- RTC reloj,

- NVRAM (alimentada por bateria),

- Generador de señal de reloj de dos canales sincronizados:

- Reloj de sistema 4/8/12/16/20 MHz (2/4/6/8/10 MHz Z80 CPU),

- Reloj de EXDOS 8/9.6/10/12/13.33/16 MHz,

- Pantalla LCD u OLED (2x16 caracteres),

- LED RGB para señalar por colores la frecuencia de CPU seleccionada:

- 2MHz azul,

- 4MHz verde,

- 6MHz amarillo,

- 8MHz naranja,

- 10MHz rojo,

- Opcionalmente sensor de temperatura para NICK,

- Configurable por codificador rotatorio o por software.

Caracteristicas

Comunicación con la tarjeta

| Dirección I/O | Sentido | Contenido |

|---|---|---|

| 0x7E | escritura | Selección de dirección NVRAM |

| lectura | registro de estado de la tarjeta | |

| 0x7F | escritura | datos NVRAM |

| lectura |

Registro de estado

| Bit | Nombre | Contenido |

|---|---|---|

| 0 | EP RFSH | el microcontrolador ha modificado la memoria NVRAM (el EP debería comprobarlo, y la lectura del puerto de datos NVRAM pondrá a cero este bit) |

| 1 | CLK Sys Ready | system clock synchronized to the current setting |

| 2 | CLK EXDOS Ready | EXDOS clock synchronized to the current setting |

| 3 | RTC RQ | card microcontroller requests access to NVRAM memory |

| 4 | RTC RFSH | EP saved new data into the NVRAM memory (the read by card microcontroller resets this bit) |

| 5 | reserved | for now always '0' |

| 6 | S0 | microcontroller status bit 0 (1 = temperature reading completed) |

| 7 | S1 | microcontroller status bit 1 (not used yet) |

Config registers

| Address | Bits | Content | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| NVRAM | CPLD | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x7F *) | NA | Device ID | Dream Turbo Card ID is 44h | |||||||

| 0x7E *) | NA | Hw batch no. | Hw serial no. | Hardware serial number | ||||||

| 0x7D *) | NA | Hw ver. mj. | Hw ver. mn. | Hardware version (major.minor) | ||||||

| 0x7C *) | NA | Fw ver. mj. | Fw ver. mn. | Firmware version (major.minor) | ||||||

| 0x7B *) | NA | DSP | LS | RAM2 | uC | TEMP | Flash | Features (below) | ||

| 0x7A | 3 | Memory mode | EXDOS clock select | System clock select | Memory bank mode, selection of clocks (below) | |||||

| 0x79 | 2 | CLK link | Flash.6 | Flash.5 | Flash.4 | Flash.3 | Flash.2 | Flash.1 | Flash.0 | Disabling flash memory banks, bit N=1 Flash bank N disable |

| 0x78 *) | 1 | S1 | S0 | LCD bias | uC status bits & LCD contrast | |||||

| 0x77 *) | 0 | LCD backlight | LED blue | LED green | LED red | LCD backlight and RGB LED control | ||||

| 0x76 *) | NA | Current temperature | Current NICK temperature | |||||||

| 0x75 | NA | Temperature limit | NICK temperature level for the alarm (0 = alarm off) | |||||||

*) read-only, data will be always overwritten by the card microcontroller,

| Feature | Description | Value | Type |

|---|---|---|---|

| Flash | Flash chip type | 00 | Microchip SST39SF040 |

| 01 | . | ||

| 10 | . | ||

| 11 | . | ||

| TEMP | temperature sensor type | 00 | none |

| 01 | Dallas DS18B20 | ||

| 10 | Analog Devices TMP03/04 | ||

| 11 | Analog Devices TMP05/06 | ||

| uC | microcontroller type | 0 | MCS51 |

| 1 | AVR | ||

| RAM2 | RAM capacity | 0 | 1 MB |

| 1 | 2 MB | ||

| LS | sound transducer | 0 | buzzer or none |

| 1 | loudspeaker | ||

| DSP | display type | 0 | OLED |

| 1 | LCD |

Memory map

MT is MICROTEAM card.

| Mode 0 (default) | ||||

|---|---|---|---|---|

| BANK | x0-x3 | x4-x7 | x8-xB | xC-xF |

| 0x | Flash.7 | CART | EPNET | EPNET |

| 1x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| 2x | MT Flash | MT Flash | MT Flash | MT Flash |

| 3x | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| 4x | MT DRAM1 | MT DRAM1 | MT DRAM1 | MT DRAM1 |

| 5x | MT DRAM2 | MT DRAM2 | MT DRAM2 | MT DRAM2 |

| 6x | Flash.0 | Flash.1 | Flash.2 | Flash.3 |

| 7x | Flash.4 | Flash.5 | Flash.6 | RAM1.F |

| 8x | RAM2.0 | RAM2.1 | RAM2.2 | RAM2.3 |

| 9x | RAM2.4 | RAM2.5 | RAM2.6 | RAM2.7 |

| Ax | RAM2.8 | RAM2.9 | RAM2.A | RAM2.B |

| Bx | RAM2.C | RAM2.D | RAM2.E | RAM2.F |

| Cx | RAM1.0 | RAM1.1 | RAM1.2 | RAM1.3 |

| Dx | RAM1.4 | RAM1.5 | RAM1.6 | RAM1.7 |

| Ex | RAM1.8 | RAM1.9 | RAM1.A | RAM1.B |

| Fx | RAM1.C | RAM1.D | RAM1.E | VRAM |

| Mode 1 (no RAM2) | ||||

|---|---|---|---|---|

| BANK | x0-x3 | x4-x7 | x8-xB | xC-xF |

| 0x | Flash.7 | CART | EPNET | EPNET |

| 1x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| 2x | MT Flash | MT Flash | MT Flash | MT Flash |

| 3x | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| 4x | MT DRAM1 | MT DRAM1 | MT DRAM1 | MT DRAM1 |

| 5x | MT DRAM2 | MT DRAM2 | MT DRAM2 | MT DRAM2 |

| 6x | Flash.0 | Flash.1 | Flash.2 | Flash.3 |

| 7x | Flash.4 | Flash.5 | Flash.6 | RAM1.F |

| 8x | not used | not used | not used | not used |

| 9x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| Ax | MT Flash | MT Flash | MT Flash | MT Flash |

| Bx | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| Cx | RAM1.0 | RAM1.1 | RAM1.2 | RAM1.3 |

| Dx | RAM1.4 | RAM1.5 | RAM1.6 | RAM1.7 |

| Ex | RAM1.8 | RAM1.9 | RAM1.A | RAM1.B |

| Fx | RAM1.C | RAM1.D | RAM1.E | VRAM |

| Mode 2 (no Flash) | ||||

|---|---|---|---|---|

| BANK | x0-x3 | x4-x7 | x8-xB | xC-xF |

| 0x | Flash.7 | CART | EPNET | EPNET |

| 1x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| 2x | MT Flash | MT Flash | MT Flash | MT Flash |

| 3x | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| 4x | MT DRAM1 | MT DRAM1 | MT DRAM1 | MT DRAM1 |

| 5x | MT DRAM2 | MT DRAM2 | MT DRAM2 | MT DRAM2 |

| 6x | RAM2.8 | RAM2.9 | RAM2.A | RAM2.B |

| 7x | RAM2.C | RAM2.D | RAM2.E | RAM1.F |

| 8x | RAM2.0 | RAM2.1 | RAM2.2 | RAM2.3 |

| 9x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| Ax | MT Flash | MT Flash | MT Flash | MT Flash |

| Bx | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| Cx | RAM1.0 | RAM1.1 | RAM1.2 | RAM1.3 |

| Dx | RAM1.4 | RAM1.5 | RAM1.6 | RAM1.7 |

| Ex | RAM1.8 | RAM1.9 | RAM1.A | RAM1.B |

| Fx | RAM1.C | RAM1.D | RAM1.E | VRAM |

| Mode 3 (no Flash & RAM2) | ||||

|---|---|---|---|---|

| BANK | x0-x3 | x4-x7 | x8-xB | xC-xF |

| 0x | Flash.7 | CART | EPNET | EPNET |

| 1x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| 2x | MT Flash | MT Flash | MT Flash | MT Flash |

| 3x | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| 4x | MT DRAM1 | MT DRAM1 | MT DRAM1 | MT DRAM1 |

| 5x | MT DRAM2 | MT DRAM2 | MT DRAM2 | MT DRAM2 |

| 6x | not used | not used | not used | not used |

| 7x | not used | not used | not used | RAM1.F |

| 8x | not used | not used | not used | not used |

| 9x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| Ax | MT Flash | MT Flash | MT Flash | MT Flash |

| Bx | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| Cx | RAM1.0 | RAM1.1 | RAM1.2 | RAM1.3 |

| Dx | RAM1.4 | RAM1.5 | RAM1.6 | RAM1.7 |

| Ex | RAM1.8 | RAM1.9 | RAM1.A | RAM1.B |

| Fx | RAM1.C | RAM1.D | RAM1.E | VRAM |

Clock selection

| SELECT | System clock | CPU clock | EXDOS clock |

|---|---|---|---|

| 0 | 8 MHz | 4 MHz | 8 MHz |

| 1 | 12 MHz | 6 MHz | 9.6 MHz |

| 2 | 16 MHz | 8 MHz | 10 MHz |

| 3 | 20 MHz | 10 MHz | 12 MHz |

| 4 | 4 MHz | 2 MHz | 13.33 MHz |

| 5 | 8 MHz | 4 MHz | 16 MHz |

| 6 | 8 MHz | 4 MHz | 8 MHz |

| 7 | 8 MHz | 4 MHz | 8 MHz |

Minimum value of system clock in "linked mode"

When we raise the EXDOS clock frequency, the data from the FDC controller will be sent faster.

In some cases, the processor clocked by a lower frequency may not be able to process transmitted data.

To prevent this situation, it is possible to activate the "linking" mode of clock signals.

In this mode the card's microcontroller will ensure that the processor's clock frequency is not less than the minimum frequency at which the processor is able to keep pace with data from the FDC controller.

| Selected system clock | 4 MHz | 8 MHz | 12 MHz | 16 MHz | 20 MHz | |||||

|---|---|---|---|---|---|---|---|---|---|---|

| Selected EXDOS clock | Actual frequency (System/CPU) | |||||||||

| 8 MHz | 8 MHz | 4 MHz | 8 MHz | 4 MHz | 12 MHz | 6 MHz | 16 MHz | 8 MHz | 20 MHz | 10 MHz |

| 9.6 MHz | 8 MHz | 4 MHz | 8 MHz | 4 MHz | 12 MHz | 6 MHz | 16 MHz | 8 MHz | 20 MHz | 10 MHz |

| 10 MHz | 8 MHz | 4 MHz | 8 MHz | 4 MHz | 12 MHz | 6 MHz | 16 MHz | 8 MHz | 20 MHz | 10 MHz |

| 12 MHz | 12 MHz | 6 MHz | 12 MHz | 6 MHz | 12 MHz | 6 MHz | 16 MHz | 8 MHz | 20 MHz | 10 MHz |

| 13.33 MHz | 12 MHz | 6 MHz | 12 MHz | 6 MHz | 12 MHz | 6 MHz | 16 MHz | 8 MHz | 20 MHz | 10 MHz |

| 16 MHz | 16 MHz | 8 MHz | 16 MHz | 8 MHz | 16 MHz | 8 MHz | 16 MHz | 8 MHz | 20 MHz | 10 MHz |

How to install

DTC is a complex interface. The installation requires interference with the computer.

The author has made every effort to make the interface as reliable and safe to use as possible. However,

You make any modifications inside of your equipment at your own risk !

What you need

- Dream Turbo Card

- L-connector

- new Z80 processor suitable for work at clock speeds of at least 10 MHz (eg. Z84C0010P, Z84C0020P)

Enterprise mainboard preparation

- desolder and remove internal 64KB RAM memory module (Enterprise 128 only)

- desolder the Z80 processor

Instalación del conector L

Primera puesta en marcha

Enlaces

Hilo en el foro Enterprise Forever 6Mhz and more...