Difference between revisions of "Dream Turbo Card by pear"

From Enterprise Wiki

m (→Features) |

(→Memory map) |

||

| Line 53: | Line 53: | ||

{|class="wikitable" | {|class="wikitable" | ||

| − | ! | + | !colspan=5|Mode 0 (default) |

| − | |||

| − | |||

|- | |- | ||

| − | !scope=" | + | !scope="row"| ||style="width: 70px; text-align:center"|x0-x3||style="width: 70px; text-align:center"|x4-x7||style="width: 70px; text-align:center"|x8-xB||style="width: 70px; text-align:center"|xC-xF |

| − | | | ||

|- | |- | ||

| − | !scope="col"| | + | !scope="col"|0x |

| − | | | + | |style="text-align:center; background-color: #00b0f0"|Flash.7||style="text-align:center; background-color: #ed7d31"|CART |

| + | |style="text-align:center; background-color: #cc0099"|EPNET||style="text-align:center; background-color: #cc0099"|EPNET | ||

|- | |- | ||

| − | !scope="col"| | + | !scope="col"|1x |

| − | | | + | |style="text-align:center; background-color: #ffccff"|MT SRAM1||style="text-align:center; background-color: #ffccff"|MT SRAM1 |

| + | |style="text-align:center; background-color: #ffccff"|MT SRAM1||style="text-align:center; background-color: #ffccff"|MT SRAM1 | ||

|- | |- | ||

| − | !scope="col"| | + | !scope="col"|2x |

| − | | | + | |style="text-align:center; background-color: #ff99cc"|MT Flash||style="text-align:center; background-color: #ff99cc"|MT Flash |

| + | |style="text-align:center; background-color: #ff99cc"|MT Flash||style="text-align:center; background-color: #ff99cc"|MT Flash | ||

| + | |- | ||

| + | !scope="col"|3x | ||

| + | |style="text-align:center; background-color: #ff6699"|MT SRAM2||style="text-align:center; background-color: #ff6699"|MT SRAM2 | ||

| + | |style="text-align:center; background-color: #ff6699"|MT SRAM2||style="text-align:center; background-color: #ff6699"|MT SRAM2 | ||

| + | |- | ||

| + | !scope="col"|4x | ||

| + | |style="text-align:center; background-color: #ffc000"|MT DRAM1||style="text-align:center; background-color: #ffc000"|MT DRAM1 | ||

| + | |style="text-align:center; background-color: #ffc000"|MT DRAM1||style="text-align:center; background-color: #ffc000"|MT DRAM1 | ||

| + | |- | ||

| + | !scope="col"|5x | ||

| + | |style="text-align:center; background-color: #ffff00"|MT DRAM2||style="text-align:center; background-color: #ffff00"|MT DRAM2 | ||

| + | |style="text-align:center; background-color: #ffff00"|MT DRAM2||style="text-align:center; background-color: #ffff00"|MT DRAM2 | ||

| + | |- | ||

| + | !scope="col"|6x | ||

| + | |style="text-align:center; background-color: #0070c0"|Flash.0||style="text-align:center; background-color: #0070c0"|Flash.1 | ||

| + | |style="text-align:center; background-color: #0070c0"|Flash.2||style="text-align:center; background-color: #0070c0"|Flash.3 | ||

| + | |- | ||

| + | !scope="col"|7x | ||

| + | |style="text-align:center; background-color: #0070c0"|Flash.4||style="text-align:center; background-color: #0070c0"|Flash.5 | ||

| + | |style="text-align:center; background-color: #0070c0"|Flash.6||style="text-align:center; background-color: #00b050"|RAM1.F | ||

| + | |- | ||

| + | !scope="col"|8x | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.0||style="text-align:center; background-color: #92d050"|RAM2.1 | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.2||style="text-align:center; background-color: #92d050"|RAM2.3 | ||

| + | |- | ||

| + | !scope="col"|9x | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.4||style="text-align:center; background-color: #92d050"|RAM2.5 | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.6||style="text-align:center; background-color: #92d050"|RAM2.7 | ||

| + | |- | ||

| + | !scope="col"|Ax | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.8||style="text-align:center; background-color: #92d050"|RAM2.9 | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.A||style="text-align:center; background-color: #92d050"|RAM2.B | ||

| + | |- | ||

| + | !scope="col"|Bx | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.C||style="text-align:center; background-color: #92d050"|RAM2.D | ||

| + | |style="text-align:center; background-color: #92d050"|RAM2.E||style="text-align:center; background-color: #92d050"|RAM2.F | ||

| + | |- | ||

| + | !scope="col"|Cx | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.0||style="text-align:center; background-color: #00b050"|RAM1.1 | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.2||style="text-align:center; background-color: #00b050"|RAM1.3 | ||

| + | |- | ||

| + | !scope="col"|Dx | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.4||style="text-align:center; background-color: #00b050"|RAM1.5 | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.6||style="text-align:center; background-color: #00b050"|RAM1.7 | ||

| + | |- | ||

| + | !scope="col"|Ex | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.8||style="text-align:center; background-color: #00b050"|RAM1.9 | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.A||style="text-align:center; background-color: #00b050"|RAM1.B | ||

| + | |- | ||

| + | !scope="col"|Fx | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.C||style="text-align:center; background-color: #00b050"|RAM1.D | ||

| + | |style="text-align:center; background-color: #00b050"|RAM1.E||style="text-align:center; background-color: #ff0000"|VRAM | ||

|} | |} | ||

[[File:DTCMemMap.png]] | [[File:DTCMemMap.png]] | ||

| + | |||

====Clock selection==== | ====Clock selection==== | ||

{|class="wikitable" | {|class="wikitable" | ||

Revision as of 18:20, 6 January 2018

Contents

Brief information

Internal memory card and switched clock generators.

Specification

- 1 MB SRAM, optionally 2 MB, in banks of 64KB,

- 512 KB FlashROM, 8 banks of 64 KB with the option of individual switching off, EXOS in bank 7 (always on),

- RTC clock,

- NVRAM (battery backup),

- two-channel synchronized clock signal generator:

- system clock 4/8/12/16/20 MHz (2/4/6/8/10 MHz Z80 CPU),

- EXDOS clock 8/9.6/10/12/13.33/16 MHz

- LCD or OLED display (2x16 chars),

- RGB LED to signal by colors the selected CPU clock:

- 2MHz blue,

- 4MHz green,

- 6MHz yellow,

- 8MHz orange,

- 10MHz red,

- optional temperature sensor for NICK,

- configured by rotary encoder or by software.

Features

Status register

Config registers

| Address | Bits | Content | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| NVRAM | CPLD | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x7F | 3 | Memory mode | EXDOS clock | System clock | Memory bank mode, selection of clocks (below) | |||||

| 0x7E | 2 | unused | Flash.6 | Flash.5 | Flash.4 | Flash.3 | Flash.2 | Flash.1 | Flash.0 | Disabling flash memory banks, bit N=1 Flash bank N disable |

| N/A | 1 | LCD bias | LCD contrast | |||||||

| N/A | 0 | LCD backlight | LED blue | LED green | LED red | LCD backlight and RGB LED control | ||||

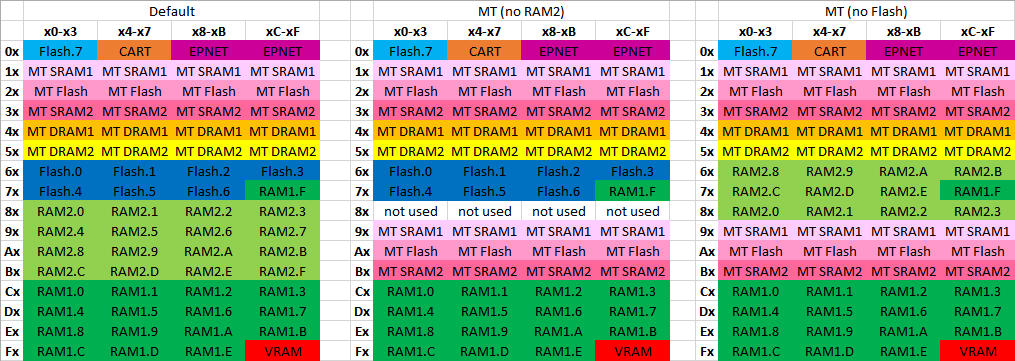

Memory map

MT is MICROTEAM card.

| Mode 0 (default) | ||||

|---|---|---|---|---|

| x0-x3 | x4-x7 | x8-xB | xC-xF | |

| 0x | Flash.7 | CART | EPNET | EPNET |

| 1x | MT SRAM1 | MT SRAM1 | MT SRAM1 | MT SRAM1 |

| 2x | MT Flash | MT Flash | MT Flash | MT Flash |

| 3x | MT SRAM2 | MT SRAM2 | MT SRAM2 | MT SRAM2 |

| 4x | MT DRAM1 | MT DRAM1 | MT DRAM1 | MT DRAM1 |

| 5x | MT DRAM2 | MT DRAM2 | MT DRAM2 | MT DRAM2 |

| 6x | Flash.0 | Flash.1 | Flash.2 | Flash.3 |

| 7x | Flash.4 | Flash.5 | Flash.6 | RAM1.F |

| 8x | RAM2.0 | RAM2.1 | RAM2.2 | RAM2.3 |

| 9x | RAM2.4 | RAM2.5 | RAM2.6 | RAM2.7 |

| Ax | RAM2.8 | RAM2.9 | RAM2.A | RAM2.B |

| Bx | RAM2.C | RAM2.D | RAM2.E | RAM2.F |

| Cx | RAM1.0 | RAM1.1 | RAM1.2 | RAM1.3 |

| Dx | RAM1.4 | RAM1.5 | RAM1.6 | RAM1.7 |

| Ex | RAM1.8 | RAM1.9 | RAM1.A | RAM1.B |

| Fx | RAM1.C | RAM1.D | RAM1.E | VRAM |

Clock selection

| DS1 | DS2 | Work mode |

|---|---|---|

| ON | ON | EnterMice native mouse mode |

| OFF | ON | BoxSoft compatible mouse mode. The two main buttons are swapped. Main now is the right one. |

| OFF | OFF | EnterMice joystick mode (Movement made to the mouse is redirected to the input of Joystick 1, and that port is disabled) |

| ON | OFF | not used (in fact EnterMice as joystick on KB K column) |

How to install

Links

Thread on the Enterprise Forever forum 6Mhz and more...